¿Qué

es erróneo en una implementación de un solo ciclo?

Por definición, el ciclo de reloj debe tener la misma duración para cada instrucción de este diseño de un único ciclo, y el CPI tendrá que ser 1. Por supuesto, el ciclo de reloj está determinado por el camino más largo posible de la máquina. Este camino es ciertamente casi una instrucción de carga, que utiliza cinco unidades funciona les en serie: la memoria de instrucciones, el archivo de registros, la ALU, la memoria de datos y el archivo de registros. Aunque el CPI es 1, el rendimiento global de una implementación de un solo reloj probablemente no sea muy bueno, ya que algunos tipos de instrucciones pueden realizarse en un ciclo de reloj más corto.

La penalización por utilizar el diseño de un solo ciclo de reloj con un ciclo de reloj fijo es no trivial, pero puede considerarse aceptable para este pequeño repertorio de instrucciones. Sin embargo, si tratamos de implementar la unidad de punto flotante o un repertorio de instrucciones con instrucciones más complejas, o utilizar técnicas de implementación más sofisticadas, este diseño de un solo ciclo de reloj no funcionaría bien de ninguna manera.

Análogamente, si tuviésemos una máquina con modos de direccionamiento y operaciones más potentes, las instrucciones podrían variar desde tres o cuatro retardos de unidades funcionales a decenas o cientos de retardos de unidades funcionales. Además, como debemos asumir que el ciclo de reloj es igual al retardo del peor caso para todas las instrucciones, no podemos utilizar técnicas de implementación que reduzcan el retardo del caso común si no se mejora la duración del ciclo del peor caso. ¡ Por ejemplo, tal restricción haría que una caché fuese inútil en esta máquina! Una implementación de un solo ciclo entonces viola nuestro principio clave de diseño de hacer rápido el caso común.demás, con esta implementación de un solo ciclo, cada unidad funcional puede utilizarse solo una vez por reloj; por tanto, algunas unidades funcionales deben estar duplicadas, elevando el coste de la implementación.

Podemos evitar estas dificultades utilizando técnicas de implementación que tengan un ciclo de reloj más corto -obtenido a partir de los retardos de las unidades funcionales básicas- y que requieran múltiples ciclos de reloj para cada instrucción. La siguiente sección explora este esquema alternativo de implementación: multiples ciclos de reloj.

En una implementación multiciclo, cada paso de la ejecución empleará un ciclo de reloj. La implementación multiciclo permite que una unidad funcional sea utilizada más de una vez por instrucción, mientras se utilice en diferentes ciclos de reloj. Esto puede ayudar a reducir la cantidad de hardware necesario. La posibilidad de que las instrucciones empleen diferentes números de ciclos de reloj y la posibilidad de compartir unidades funcionales en la ejecución de una única instrucción son las mayores ventajas del diseño multiciclo.

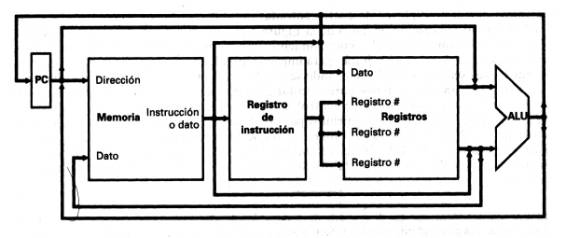

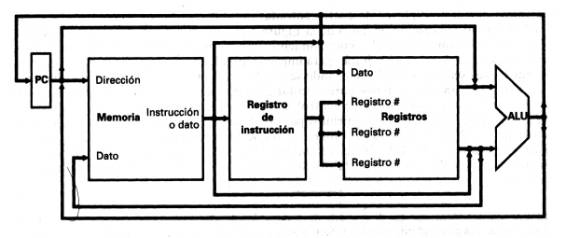

Figura 5.34. Visión de alto nivel del camino de datos multiciclo. Este cuadro muestra los elementos clave del camino de datos: una unidad de memoria compartida, una única ALU compartida entre las instrucciones, y los caminos de datos para conectar estas unidades compartidas.

·

Se utiliza una sola unidad de memoria para

instrucciones y datos.

·

Se utiliza un registro para guardar la instrucción

una vez que se lee. Este Registro de instrucción (IR) se necesita porque la

memoria puede ser reutilizada para acceder más tarde al dato en la ejecución

de la instrucción.

Hay una sola ALU, en lugar de una ALU y dos sumadores.

Como se utiliza una memoria para instrucciones y datos, necesitamos un

multiplexor para seleccionar entre las dos posibles fuentes de una dirección de

memoria, a saber, el PC (para acceder a la instrucción) y el resultado de la

ALU (para acceder a los datos). Compartir la ALU requiere la introducción de un

multiplexor para la primera entrada de la ALU, que puede ser o un registro o el

PC, y el cambio del multiplexor de dos entradas de la segunda entrada de la ALU

por uno de cuatro entradas, que requiere dos entradas adicionales: la constante

4 (utilizada para incrementar el PC) y el signo extendido y campo de

desplazamiento «desplazado» (shifted offset) utilizado en el cálculo de la

dirección del salto. La Figura 5:35 muestra los detalles del camino de datos

con estos multiplexores adicionales. En total, introduciendo un registro y tres

multiplexores, podemos reducir el número de unidades de memoria de dos a una y

eliminar dos sumadores. Como los registros y multiplexores son bastante pequeños,

se podría lograr una reducción sustancial del coste del hardware.

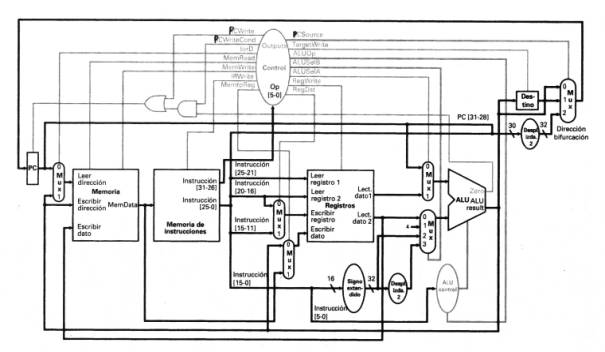

Como el camino de datos mostrado en la Figura 5.35 necesita múltiples

ciclos de reloj por instrucción, se necesitará un conjunto diferente de señales

de control. Necesitaremos una señal de escritura para cada uno de los elementos

de estado: la memoria, el PC, los registros de propósito general y el Registro

de instrucción. También necesitaremos una señal de lectura para la memoria.

Podemos utilizar la unidad de control de la ALU de los ejemplos anteriores

(Figuras 5.17 y 5.18) para controlar también aquí la ALU Finalmente, cada uno

de los dos multiplexores de dos entradas requiere una sola línea de control,

mientras que el multiplexor de cuatro entradas necesita dos líneas de control.

La Figura 5.36 muestra el camino de datos de la Figura 5.35 con estas líneas de

control añadidas. Una vez que examinemos el secuenciamiento de las

instrucciones veremos qué señales adicionales de control se necesitarán para

implementar algunas instrucciones, específicamente altos; estas señales

controlarán cuando se escriba en el PC y el valor que se escriba en él.

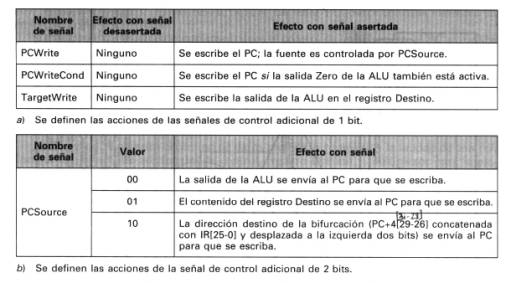

Antes de examinar los pasos para ejecutar cada instrucción, es útil

establecer informalmente qué efectúan las señales de control, cuáles hemos añadido,

qué tienen cuando son asertadas y desasertadas (como hicimos para el diseño de

un solo ciclo en la Figura 5.21 de la página 260). La Figura 5.37 muestra lo

que hace cada señal de control cuando es asertada y desasertada. Las señales

de control de un solo bit aparecen en la tabla a) de la figura, y las señales

de control de dos bits, ALUSelB y ALUOp, están definidas en la tabla b).

Elaboración: Para reducir el número de líneas de señales que interconectan las unidades funcionales, los diseñadores pueden utiIizar buses compartidos. Un bus compartido es un conjunto de líneas que conectan múItipIes unidades; en muchos casos, incluyen múItipIes fuentes que pueden colocar datos en el bus y múltiples lecturas del valor. De iguaI manera que reducimos el número de unidades funcionaIes para el camino de datos, podemos reducir el número de buses que interconectan estas unidades compartiendo los buses. Por ejemplo, hay cinco fuentes que van a la ALU; sin embargo, sólo dos de ellas son necesarias en cualquier instante de tiempo. Asi se puede utilizar un par de buses para los valores que se envían a la ALU. En Iugar de coIocar un gran multiplexor enfrente de Ia ALU, un diseñador puede utilizar un bus compartido y después asegurar que solamente una de Ias fuentes está controIando eI bus en cualquier punto.

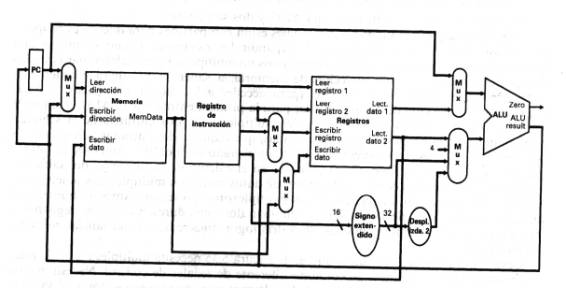

Figura 5.35. El camino de datos multiestado para MIPS maneja todas las instrucciones básicas. Lo que se ha añadido con respecto al camino de datos de un solo reloj es: un multiplexor para la dirección de lectura de memoria, un multiplexor para la entrada superior de la ALU, y una expansión del multiplexor de la entrada inferior de la ALU por un selector de cuatro entradas. Las pequeñas adiciones nos permiten eliminar dos sumadores y una unidad de memoria.

|

|

Figura 5.36. El camino de datos

multiciclo con las líneas de control mostradas. Las señales ALUOp y

ALUSelB son señales de control de 2 bits, mientras que las demás líneas de

control corresponden a señales de 1 bit. La señal MemRead se ha desplazado a

la parte superior de la unidad de memoria para simplificar las figuras.

|

|

Figura 5.37. Acción causada por la inicialización de cada señal de control. La

tabla a) describe las señales de control de 1 bit, mientras que la tabla b)

describe las señales de 2 bits. Sólo aquellas líneas de control que afectan a

los multiplexores tienen una acción cuando son O. Esta información es análoga

a la de la Figura 5.21 de la página 260 para el camino de datos de un solo

ciclo. pero añade las nuevas líneas de control (ALUSeIA, lorD, IRWrite y

ALUSelB) y elimina las líneas de control que no se van a usar más o que han

sido sustituidas (Jump [Bifurcación], Branch [Salto] y ALUSrc).

Dado este camino de datos, necesitamos examinar lo que ocurriría en cada

ciclo de reloj de la ejecución multiciclo, ya que esto determinará los

elementos adicionales del camino de datos (registros temporales, por ejemplo) y

las señales de control adicionales que pueden ser necesarias: Necesitaremos

introducir un registro que contenga un valor de señal siempre que se cumplan

las dos condiciones siguientes:

1. La señal se calcula en un ciclo

de reloj y se utiliza en otro:

2.

Las entradas al bloque funcional de donde sale esta señal pueden cambiar antes

que

la señal se escriba en un elemento de estado.

Por ejemplo, necesitamos almacenar la instrucción en el Registro de

instrucción, porque la unidad funcional (la memoria) que produce el valor

cambia su salida antes que completemos todos los usos de los campos de la

instrucción. Por otro lado, cuando la ALU se utiliza en una instrucción tipo

R, no necesitamos almacenar su salida, aunque no se utilice ésta hasta el

siguiente ciclo de reloj. Esto es porque la salida de la ALU no cambia (es

decir, es estable) durante el ciclo de reloj cuando se escribe en el archivo de

registros. La salida de la ALU es estable porque las entradas a la ALU provienen

del archivo de registros, y la salida del archivo de registros está determinada

por los campos rs y rt del Registro de instrucción, que es estable porque es un

elemento de estado escrito sólo una vez por ejecución de instrucción. Así,

las unidades funcionales desde el archivo de registros hasta la ALU constituyen

un bloque de lógica combinacional, cuyas entradas provienen del Registro de

instrucción (un elemento de estado) y cuya salida se escribe en el archivo de

registros (también un elemento de estado).

Nuestro objetivo al descomponer la ejecución en ciclos de

reloj es para equilibar la cantidad de trabajo realizado en cada ciclo, para

minimizar la duración del ciclo de reloj. Podemos descomponer la ejecución en

cinco pasos, cada uno de los cuales necesita un ciclo de reloj, que

aproximadamente estarán equilibrados en duración. Por ejemplo, restringiremos

cada paso a que como máximo contenga una operación de la ALU, o un acceso al

archivo de registros, o un acceso a memoria. Con esta restricción, el ciclo de

reloj puede ser tan corto como la más larga de estas operaciones:

En el camino de datos de un solo ciclo cada instrucción debía utilizar un conjunto de elementos del camino de datos para su ejecución. Muchos elementos del camino de datos operan en serie, utilizando la salida de otro elemento como entrada. Algunos elementos del camino de datos operan en paralelo; por ejemplo,. se incrementa el PC y se lee la instrucción al mismo tiempo. Una situación similar exlste en el camino de datos multiciclo. T odas las operaciones listadas en un paso se presentan en paralelo en un ciclo de reloj, mientras que los pasos siguientes operan en serie en diferentes ciclos de reloj. La limitación de una operación de la ALU, un acceso a memoria, o un acceso al archivo de registros determina qué puede rellenar un paso. Los cinco pasos de ejecución y sus acciones se dan a continuación.

1. Paso de búsqueda de

instrucción:

Busca la instrucción de

memoria e incrementa el contador de programa.

IR=Memoria[PC];

PC=PC+4;

Operación: Envía el PC a memoria como dirección, realiza una lectura y busca la instrucción en el Registro de instrucción (IR), donde estará almacenada. Para implementar este paso necesitaremos asertar las señales de control MemRead e IRW rite, e inicializar IorD a 0 para seleccionar el PC como fuente de la dirección. En esta etapa también incrementamos el PC en 4, lo que requiere inicializar la señal ALUSelB a 01, la señal ALUSelA a 0 y ALUOp a 00 (para hacer que la ALU sume). Finalmente, hay que almacenar otra vez en el PC la dirección de la instrucción incrementada; añadiremos este camino y el control, cuando hayamos determinado el control completo para el PC, incluyendo los saltos. El incremento del PC y el acceso a la memoria de instrucciones se pueden realizar en paralelo.

2:

Paso de decodificación de la instrucción y búsqueda de registros:

En el paso anterior y en éste, todavía no sabemos de qué instrucción

se trata, por ello solamente podemos realizar acciones que son o aplicables a

todas las instrucciones (tal como la búsqueda de la instrucción en el paso 1),

o que no son perjudiciales, en el caso de que la instrucción no sea la que

pensamos que podria ser. Por ello, en este paso podemos leer los dos registros

indicados por los campos de instrucción rs y rt, ya que no es perjudicial

leerlos aun cuando no sea necesario. El contenido de los registros puede ser

necesario en etapas posteriores, así los nombramos A y B en la descripción

siguiente. No es necesario guardar en registros temporales las salidas de los

registros, ya que las entradas a los números de registro (y por tanto las

salidas de los datos de los registros) no se cambian durante la ejecución de la

instrucción:

También calcularemos con la ALU la dirección destino del salto, que tampoco es perjudicial porque podemos ignorar el valor si la instrucción no se materializa en un salto: Como no sabemos si esta instrucción va a realizar o no el salto y porque necesitamosutilizar la ALU para otros propósitos en pasos posteriores, debemos guardar la dirección destino del salto en un nuevo registro que llamamos Target (Destino): (Mostraremos el camino de datos y control revisados una vez que hayamos completado los cinco pasos:) La realización anticipada de estas acciones « optimistas» tienen el beneficio de decrementar el número de ciclos de reloj necesarios para ejecutar una instrucción. Podemos hacer anticipadamente estas acciones optimistas debido a la regularidad de los formatos de instrucción. Por ejemplo, si la instrucción tiene dos entradas de registro, están siempreen los campos rs y rt; y si la instrucción es un salto, el desplazamiento se forma siempre con los 16 bits de orden inferior.

A=Registro[IR[25-21]];

B=Registro[IR[20-16]];

Destino=PC+(signo-extendido ( IR[15-0])<< 2);

Operación: Se accede al archivo de registros para leer los registros utilizando los campos rs y rt; esto no requiere inicializar ninguna línea de control. Se calcula la dirección destino del salto y se almacena en Destino. Esto requiere la inicialización de ALUSelB al valor 11 (para que el campo de desplazamiento esté con el signo extendido y desplazado), ALUSelA a 0 y ALUOp a 00. Además para añadir el registro Destino, necesitaremos añadir unas líneas de control de escritura en este registro, que debe ser asertado durante este paso. Los accesos al registro y el cálculo del destino del salto se realizan en paralelo. Después de este ciclo de reloj, la acción a tomar depende del contenido de la instrucción:

3. Ejecución, cálculo de la

dirección de memoria, o terminación del salto:

Este es el primer ciclo durante el cual la operación del camino de datos está determinada por el tipo de instrucción. En todos los casos, la ALU opera sobre los operandos preparados en el paso anterior, realizando una de las tres funciones, dependiendo del tipo de instrucción. Llamamos al resultado de la ALU ALUoutput para utilizarlo en etapas posteriores: Como las entradas a la ALU son estables, no es necesario guardar este valor en ningún registro: Sin embargo, cualquier conjunto de señales de este ciclo que afecte al resultado de la ALU debe mantenerse constante hasta que los resultados de la ALU se escriban en un registro o no se necesiten más. Especificamos la acción a tomar dependiendo de la clase de instrucción:

Referencia a memoria:

ALUoutput=A+signo-extendido (IR[15-0]);

Operación:

La ALU suma los operandos para formar la dirección de memoria: Esto requiere

inicializar ALUSelA a 1, que utilizará la primera salida del archivo de

registros como primera entrada de la ALU, e inicializar ALUSelB a 10, que hará

que la salida de la unidad de extensión de signo se utilice como segunda

entrada de la ALU. Las señales ALUOp necesitarán inicializarse a 00, forzando

a que la ALU sume.

lnstrucciones aritméticológicas (tipo R):

ALUoutput=A op B;

Operación:

La ALU realiza la operación especificada por el código de operación con los

dos registros leídos en el ciclo anterior. Esto requiere inicializar ALUSelA =

1 y ALUSelB = 00, que juntos hacen que las salidas del archivo de registros se

utilicen como entradas a la ALU. Las señales ALUOp necesitarán inicializarse a

10, para que el código de función determine las inicializaciones de las señales

de control de la ALU.

Salto:

si (A==B) PC=Destino;

Operación:

La ALU se utiliza para hacer la comparación sobre igual entre los dos registros

leídos en el paso anterior. La señal Zero que sale de la A LU se utiliza para

determinar sí hay o no hay salto. Esto requiere inicializar ALUSelA = 1 y

ALUSelB = 00, igual que para una instrucción tipo R. Las señales ALUOp

necesitarán inicializarse a 01 para realizar la resta que se utiliza en el test

de la igualdad. Es necesario disparar una señal de escritura para actualizar el

PC si la salida Zero de la ALU es asertada. Esto se especificará más tarde

cuando añadamos el control del PC.

4. Paso de acceso a memoria o

terminación de la instrucción tipo R:

Durante este paso, los accesos a memoria de las operaciones de carga y almacenamiento y operaciones aritmético-lógicas escriben su resultado. Llamamos a la salida de la memoria dato memoria (memory-data), aunque no necesita correspondencia con ningún registro, ya que su salida será estable durante el siguiente ciclo de reloj cuando se escriba en un registro.

Referencia a memoria:

dato-memoria=Memoria [ALUoutput];

o

Memoria [ALUoutput]=B;

Operación: Si la instrucción es una carga, devuelve el dato de memoria, y llamamos al valor datomemoria. Si la instrucción es un almacenamiento, entonces el dato se escribe en memoria. En cualquier caso, la dirección utilizada es la calculada durante el paso anterior y denominada ALUoutput. Las señales de control de la ALU inicializadas en el ciclo anterior deben mantenerse estables durante este ciclo: Para un almacenamiento, el operando fuente, que llamamos B, se leyó en el paso de decodificación de la instrucción y búsqueda de registros: La señal MemRead (para una carga) o MemW rite (para un almacenamiento) necesitarán ser asertadas. Además, la señal IorD se inicializa a 1 para forzar a que la dirección de memoria provenga de la ALU, en lugar del PC.

Instrucción aritméticológica (tipo R):

Reg[IR[15-11]]=ALUoutput;

Operación: Colocar el resultado de la operación de la ALU en el registro Result. La señal RegDst debe ponerse a 1 para forzar a que se utilice el campo rt (bits 15 11) para seleccionar el registro en el que se va a escribir. RegWrite debe ser asertado, y MemtoReg debe ser puesto a O, para que se escriba la salida de la ALU (en contraposición a la salida del dato de memoria). Las señales ALUSelA, ALUSelB y ALUOp no cambian desde el ciclo de reloj anterior. Recordar que como las escrituras son disparadas por flanco. la escritura del registro rd no puede afectar al dato que actualmente se está leyendo, aunque el registro destino también sea el registro fuente de la instrucción.

5. Paso de

postescritura:

Reg [IR[20-16] ]=dato-memoria;

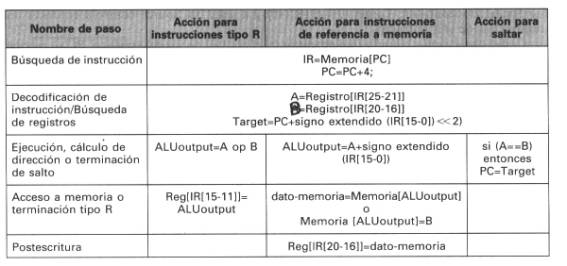

Figura 5.38. Resumen de los pasos realizados para ejecutar cualquier tipo de

instrucción. Las instrucciones necesitan de 3 a 5 pasos dee ejecución. Los

dos primeros pasos son independientes del tipo de instrucción. Después de

estos pasos, una instrucción necesita de 1 a 3 ciclos más para completarse,

dependiendo del tipo de instrucción.

Operación:

Escribe el dato cargado de memoria en el archivo de registros. Aquí

inicializamos MemtoReg = 1 para escribir el resultado de memoria, y RegWrite

para provocar una escritura, y hacemos RegDst = 0 para seleccionar el campo rt

(bits 20 16) como número de registro. De nuevo, las señales ALUSelA, ALUSelB y

ALUOp deben mantenerse estables hasta que finalice este ciclo.

La secuencia de cinco pasos se resume en la Figura 5:38: A partir de esta secuencia podemos determinar el control que debe hacerse en cada ciclo de reloj. Sin embargo, antes de que podamos diseñar la unidad de control, debemos añadir el control de escritura del PC y los multiplexores necesarios para seleccionar el valor correcto que se va a escribir en el PC, asi como el registro Target (Destino) y su control. Como implementar la instrucción de bifurcación requiere tratar por igual las dos posibilidades, incorporamos, al mismo tiempo, el control para la instrucción de bifurcación: Incluyendo la instrucción de bifurcación, hay tres posibles fuentes para el valor que se va a escribir en el PC. Éstas son:

·

ALUoutput, que es la fuente cuando se incrementa el

PC para una búsqueda secuencial de

la instrucción:

·

El registro Destino, que es la fuente cuando la

instrucción es un salto condicional que se realiza. También necesitaremos una

señal para escribir en el registro, llamada TargetWrite.

· Los 26 bits inferiores del Registro de instrucción (IR) desplazados a la izquierda dos posiciones y concatenados con los 4 bits superiores del PC, que es la fuente cuando la instrucción es una bifurcación.

Codificamos estas tres posibles fuentes utilizando una señal de control

de 2 bits, PCSource:Las tres posibilidades anteriores se codifican como 00, 01 y

10, correspondiendo a las fuentes ALUoutput (00), Target (01) e IR (10). La señal

PCSource controla entonces un multiplexor de tres entradas.

Como observamos cuando implementamos el control de un solo ciclo, el PC

se escribe de dos formas diferentes: si la instrucción no es un salto

condicional (beq), el PC se escribe incondicionalmente. Si la instrucción es un

salto condicional, el PC incrementado es sustituido por el valor en Target, sólo

si la señal de salida Zero de la ALU está bien asertada. Por tanto,

necesitamos dos señales de escritura del PC, que llamaremos PCW rite y PCW

riteCond. La señal PCW riteCond y la señal Zero de la ALU se combinan en una

puerta AND, que después se combina con PCWrite para crear una señal de

escritura para el PC.

La Figura 5.39 muestra el camino de datos multiciclo completo y la unidad

de control, incluyendo las señales adicionales de control, registro Destino y

multiplexor para implementar la actualización del PC: La Figura 5.40 muestra

los efectos de estas señales de control adicionales; junto con la Figura 5:37

estas tablas definen los efectos de todas las señales de control en el camino

de datos multiciclo de la Figura 5.39.

Definición del control

Ahora que hemos determinado cuáles son las señales de control y cuándo

deben ser asertadas, podemos implementar la unidad de control. Para diseñar la

unidad de control para el camino de datos de un solo ciclo, utilizamos un

conjunto de tablas de verdad que especificaban la inicialización de las señales

de control en base al tipo de instrucción; entonces hacíamos corresponder esas

tablas de verdad con las puertas lógicas mostradas en la Figura 5.31. Para el

camino de datos multiciclo, el control es más complejo porque la instrucción

se ejecuta en una serie de pasos. El control para el camino de datos multiciclo

debe especificar las señales que se van a inicializar en cada paso y el paso

siguiente de la secuencia.

Examinaremos dos técnicas diferentes para especificar el control. La

primera técnica está basada en máquinas de estados finitos que habitualmente

se representan de forma gráfica. La segunda técnica, llamada microprogramación,

utiliza una representación programada para el control: Ambas técnicas

representan el control en una forma que permite una implementación detallada

utilizando puertas, ROM, o PLA para ser sintetizada con un sistema CAD.

El primer método que utilizamos para especificar el control multiciclo

es una máquina de estados finitos: Una máquina de estados finitos consta de un

conjunto de estados e indicaciones sobre cómo cambian los estados. Las

indicaciones se definen por una función de estado siguiente, que hace

corresponder el estado actual y las entradas a un nuevo estado. Cuando para el

control utilizamos una máquina de estados finitos, cada estado especifica también

un conjunto de salidas que son asertadas cuando la máquina está en ese estado.

La implementación de una máquina de estados finitos habitualmente supone que

todas las salidas que no están asertadas explícitamente están desasertadas, y

la operación correcta del camino de datos con frecuencia depende del hecho de

que una sefial esté desasertada: Por ejemplo, la señal RegWrite debería estar

asertada sólo cuando se va a escribir un registro; cuando no esté explícitamente

asertada, debe ser desasertada.

Figura 5.39. Este es el camino de datos

completo para la implementación multiciclo junto con las líneas de control

necesarias. Las líneas de control de la Figura 5.36 están conectadas a la

unidad de control, están incluidos los elementos de control y del camino de

datos necesarios para efectuar los cambios en el PC. Las principales adiciones

de la Figura 5.36 incluyen: el registro Destino (en la esquina superior

derecha). el multiplexor de tres entradas utilizado para seleccionar la fuente

de un nuevo valor del PC (en la parte superior derecha), dos puertas utilizadas

para combinar las señales de escritura del PC, y las señales de control

PCSource, PCWrite. PCWriteCond

y TargetWrite. La señal PCWriteCond realiza la función AND con la

salida Zero de la ALU para decidir si se debe realizar un salto; la señal

resultante hace la operación 0R con la señal de control PCWrite. para generar

la señal de control de escritura real para el PC. Además, la salida del IR se

reorganiza para enviar los 26 bits inferiores (la dirección de salto) a la lógica

utilizada para seleccionar el siguiente PC. Estos 26 bits se concatenan con los

4 bits de orden superior del PC actual y después se desplazan 2 bits a la

izquierda (esto es equivalente a concatenar dos bits 0 de orden inferior).

Figura

5.40. El efecto de las señales de

control, que determinan cómo se escribe el PC. La tabla a) describe las señales

de control de 1 bit, que controlan la escritura del PC y del registro Destino.

La tabla b)describe la señal de 2 bits que determina la fuente del valor

escrito en el PC. Esta información. junto con el contenido de la Figura 5.37,

define la operación de todas las señales de control en el camino de datos

multiciclo.

Los controles de los multiplexores son ligeramente diferentes, ya que

seleccionan una de las entradas según sean 0 ó 1. Por tanto, en la máquina de

estados finitos, siempre especificamos la inicialización de todos los controles

de los multiplexores que utilizamos: Cuando implementamos la máquina de estados

finitos con lógica, inicializar un control a 0 puede ser el valor por defecto y

entonces puede no ser necesaria ninguna puerta. Un ejemplo sencillo de una máquina

de estados finitos aparece en el Apéndice B. y los lectores no familiarizados

con el concepto de máquina de estados finitos deberian examinar el Apéndice B

antes de proseguir.

|

|

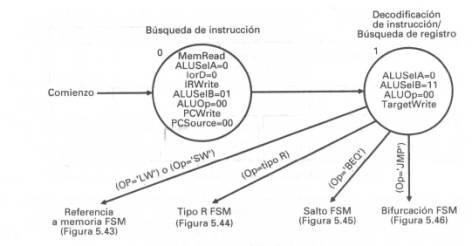

Como los dos primeros pasos de la ejecución son idénticos para cada

instrucción, los dos estados iniciales de la máquina de estados finitos serán

comunes a todas las instrucciones: Los pasos 3 al 5 difieren, dependiendo del código

de operación: Después de la ejecución del último paso para un tipo

particular de instrucción, la máquina de estados finitos volverá al estado

inicial para comenzar la búsqueda de la siguiente instrucción. La Figura 5.41

muestra esta representación abstracta de la máquina de estados finitos. Para

completar los detalles de la máquina de estados finitos, primero expandiremos

la búsqueda y la parte de decodificación de la instrucción, después

mostraremos los estados (y acciones) para los diferentes tipos de instrucción.

Figura

5.41. Visión de alto nivel del control

de la máquina de estados finitos. Los primeros pasos son independientes del

tipo de instrucción; después se utilizan una serie de secuencias, que dependen

del código de operación de la instrucción, para completar cada tipo de

instrucción. Después de completar las acciones necesarias para ese tipo de

instrucción, el control vuelve a buscar una nueva instrucción. Cada cuadro de

esta figura puede representar de uno a varios estados. La flecha rotulada

Comienzo marca el estado en el cual se comienza cuando se realiza la búsqueda

de la primera instrucción.

En mostramos los dos primeros estados de la máquina de estados finitos,

utilizando una representación gráfica tradicional. Numeramos los estados para

simplificar la explicación, aunque los números son arbitrarios. El estado 0,

correspondiente al paso 1, es el estado de arranque de la máquina.

Las señales que están asertadas en cada estado se muestran en el

estado: Los arcos entre los estados definen el estado siguiente, y están

rotulados con condiciones que seleccionan un estado siguiente especifico cuando

son posibles múltiples estados siguientes: Después del estado l, las señales

asertadas dependen del tipo de instrucción: Asi, la máquina de estados finitos

tiene cuatro arcos que salen del estado 1, correspondientes a los cuatro tipos

de instrucción: referencia a memoria, tipo R,

saltar sobre igual y bifurcación. Este proceso de saltar a diferentes estados

dependiendo de la instrucción se denomina decodificacicón, ya que la elección

del siguiente estado, y por consiguiente las acciones que siguen, dependen del

tipo de instrucción.

La parte de la máquina de estados finitos necesaria para implementar las

instrucciones de referencia a memoria se muestra en la Figura 5.43. Para las

instrucciones de referencia a memoria, el primer estado después de buscar la

instrucción y los registros calcula la dirección de memoria (estado 2). Para

calcular la dirección de memoria, la entrada a los multiplexores de la ALU debe

lnicializarse para que la primera entrada sea el registro correspondiente a rs,

mientras que la segunda entrada sea el campo de desplazamiento de signo

extendido. Después del cálculo de la dirección de memoria, la memoria debe

ser leida o escrita. Esto necesita dos estados diferentes. Si el código de

operación de la instrucción es Lw,

entonces el estado 3 (correspondiente al paso de acceso a memoria) realiza la

lectura de memoria (MemRead es asertada). Si es sw, el estado 5 realiza una escritura de memoria (MemWrite es

asertada): En ambos estados 3 y 5, la señal IorD se inicializa a 1 para forzar

que la dirección de memoria provenga de la ALU: Después de realizar una

escritura se ha completado la ejecución de la instrucción sw y el siguiente

estado es el estado O. Sin embargo, si la instrucción es una carga, es

necesario otro estado (estado 4) para escribir el resultado de la memoria en el

archivo de registros.

Figura

5.42. La parte de búsqueda y

decodificación de la instrucción de cada instrucción es idéntica. Estos

estados corresponden al cuadro superior de la máquina abstracta de estados

finitos de la Figura 5.41. En el primer estado asertamos una serie de señales

que hacen que la memoria lea una instrucción y la escriba en el Registro de

instrucción (MemRead e IRWrite, e inicializamos lorD a 0 para seleccionar PC

como dirección fuente Las señales PCWrite, PCSource, ALUSeIA, ALUOp y ALUSelB

se inicializan para calcular PC + 4 y lo almacenan en el PC En el estado

siguiente caIculamos la dirección destino del salto inicializando ALUSelB con

10 (haciendo que los 16 bits inferiores de signo extendido del IR sean enviados

a la ALU). inicializando ALUSelA a 0 y ALUOp a 00; almacenamos el resultado en

el registro Destino (utilizando TargetWrite). Hay cuatro estados siguientes que

dependen deI tipo de instrucción, el cual se conoce durante este estado. Si la

instrucción es Lw o sw, vamos a un estado. mientras que los otros arcos manejan

códigos de operación de instrucciones simples La entrada de la unidad de

control. llamada op, se utiliza para determinar cuál de estos arcos seguir.

La memoria se mantiene en modo de lectura con la misma dirección (asertando MemRead e IorD): Estas señales deben mantenerse asertadas a través de los estados porque la salida de la ALU y de la memoria no se guardan en ningún registro. Si los valores de control cambian, la salida de la ALU y memoria cambiarán, y el valor almacenado como resultado de la carga sería incorrecto. Con estos valores estándares, inicializando los controles del multiplexor MemtoReg = 1 y RegDst = 0 se enviará la salida de memoria para que se escriba en el archivo de registros, utilizando rd comonúmero de registro. Después de este estado, correspondiente al paso de postescritura, el siguiente estado es el estado 0.

Para implementar las instrucciones tipo R se requiere una máquina de

estados finito de dos estados correspondiente a los pasos de ejecución y

terminación tipo R. El estado 6 aserta ALUSelA y deja desasertadas las señales

ALUSelB; esto fuerza a que se utilicen como entradas a la ALU los dos registros

que fueron leídos del archivo de registros.

|

|

Figura

5.43. La máquina de estados finitos para

controlar instrucciones de referencia a memoria tiene cuatro estados. Estos

estados corresponden al cuadro rotulado « Instrucciones de acceso a memoria»

en la Figura 5.41. Después de realizar un calculo de direcciones de memoria. se

necesita una secuencia separada para cargar y almacenar La inicializaci6n de las

señales de control ALUSeIA. ALUSelB y ALUOp se utiliza para hacer el calculo de

la direcci6n de memoria. Estas señales deben mantenerse estables hasta que se

escriba el valor en un registro (si se trata de una carga) o en memoria (si se

trata de un almacenamiento).

Inicializando ALUOp a lO se logra que la unidad de control de la ALU

utilice el código de función para inicializar las señales de control de Ia

ALU: En el estado 7. RegWrite es asertada para hacer que se escriba en el

registro, y RegDst es asertada para hacer que el campo rd sea utilizado como número

del registro destino.

Para los saltos, solamente es necesario un estado adicional, porque su ejecución se completa durante el tercer paso de ejecución de la instrucción: Durante este estado. las señales de control que hacen que la ALU compare los valores de los dos registros deben ser inicializadas (puestas a 1), y las señales que hacen que el PC sea escrito condicionalmente con la dirección en el registro Target también se inicialicen (se ponen a 1).Para realizar la comparación es necesario que asertemos ALUSelA e inicialicemos el valor de ALUOp a 01 (forzando una resta). Para controlar la escritura del PC asertamos PCWriteCond e inicializamos PCSource a 01, que hará que el valor del registro Destino se escriba en el PC si el bit Zero que sale de la ALU está asertado.

|

|

El último tipo de instrucción es la de bifurcar; igual que el salto, sólo

requiere un único estado para completar su ejecución. En este estado, la señal

PC es asertada para hacer que el PC sea escrito. Inicializando PCSource a 10, el

valor que se escribirá será el correspondiente a los 26 bits inferiores del

Registro de instrucción concatenado con 00dos y combinado con los 4

bits superiores del PC.

|

|

En cada estado se muestran las señales que son asertadas. La función

estado siguiente depende de los bits del código de operación de la instrucción,

así rotulamos los arcos correspondientes a la función estado siguiente

sencillamente con el test del código de operación de la instrucción que se

utiliza a la entrada a la unidad de control (que es el campo del código de

operación del IR): Dada esta implementación, y sabiendo que cada estado

requiere un ciclo de reloj, podemos encontrar el CPI para una mezcla de

instrucciones típica.